SQI Flash Speicher

Speicher mit seriellen Schnittstellen wurden in der Vergangenheit primär als Datenspeicher verwendet. Der Vorteil der seriellen Schnittstelle ergibt sich dabei bezüglich der geringen Pin-Zahl und der damit verbundenen kompakten Gehäusegrösse. Durch neu implementierte Funktionen wie beispielsweise “Execute In Place” (XIP) und die Verwendung von mehreren Datenleitungen für erhöhten Datendurchsatz finden diese Speicher nun mehr und mehr Anwendungen auch als Programmspeicher für Microprozessoren. Dieses Dokument beschreibt die verschiedenen Betriebsmodi, die von den heute verfügbaren seriellen Flash Speichern unterstützt werden und die daraus resultierenden Möglichkeiten.

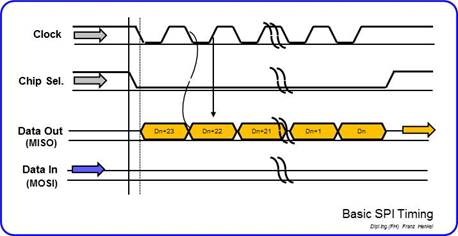

Wie beschrieben ist eine der Wurzeln von seriellen Speichern das SPI-Interface. Es benutzt vier physikalische Signale um den Datenverkehr in beiden Richtungen durchführen zu können. Diese Datenleitungen sind:

· Serieller Takt (Clock)

· Daten Eingang (MOSI)

· Daten Ausgang (MISO)

· Chip Select

Der Nachteil von SPI ist dabei die langsame Übertragungsrate mit einem Bit pro Takt. Um einen 32-Bit Befehl zu erhalten sind durch die notwendige zusätzliche Adressierung bis zu 64 Takte nötig. Auch waren die SPI-Schnittstellen in der Vergangenheit nur mit geringer Takt-Geschwindigkeit spezifiziert, was die Zugriffszeiten in Grenzen hielt.

Es gibt jedoch verschiedene Möglichkeiten die Zugriffszeiten von seriellen Speichern zu optimieren. Die Offensichtlichste besteht darin die maximale Taktrate zu erhöhen. Heute können serielle Flash Speicher mit Taktraten über 100 MHz arbeiten was die Lage zwar verbessert aber im Hinblick auf die nötige Datenbandbreite heutiger Mikroprozessoren, nicht komplett löst.

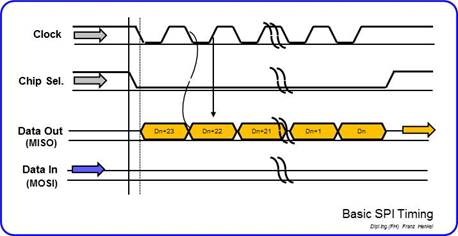

Um die Übertragungsgeschwindigkeit zu verbessern wurden die “unidirektionalen” Datenleitung des SPI Interfaces zugunsten solcher mit “bidirektionaler” Funktion geändert. Diese Änderung erhöht im ersten Moment nicht die Übertragungsgeschwindigkeit, schafft aber die Voraussetzungen weitere bidirektionale Datenleitungen parallel anzulegen.

Das normale SPI mit zwei unidirektionalen Leitung für Senden und Empfangen und dem gegenüber die parallele Speicherschnittstellen mit multiplen Adress- und Datenleitungen, markieren die Grenzen der möglichen Schnittstellen-Architekturen.

Werden in der SPI Architektur zwei bidirektionale Datenleitungen zur Verfügung gestellt verdoppelt sich der Datendurchsatz, da pro Takt zwei Bits übertragen werden können. Diese Konfiguration nennt sich “Dual SPI Mode” und ist nachfolgend schematisch im Bild dargestellt.

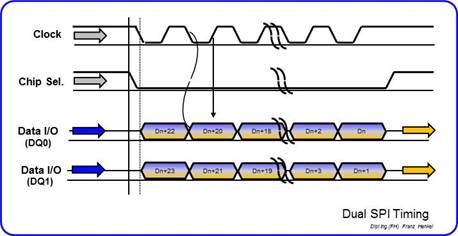

Bei einem der üblichen 8-Pin Gehäuse (8-Pin SO oder 8-pin QFN, das häufig für serielle Speicher verwendet wird), sind 4 Datenleitungen das Maximum, da die verbleibenden Pins für die Takt-Leitung, das “Chip Select” Signal und die Betriebsspannung bzw. Masse benötigt werden.

Basierend auf dieser Einteilung wurde vor einiger Zeit das SQI-Interface (Serial Quad Interface) als neuer Standard eingeführt. Es erfüllt die Anforderungen an eine geringe Pinzahl des Gehäuses, sowie den Wunsch nach einer ausreichendenden Datenbandbreite in optimierter Form.

Die Verwendung von vier parallelen Datenleitungen verbessert die Zugriffsgeschwindigkeit wesentlich (wobei die Übertragungsraten von rein parallelen Speichern immer noch nicht erreicht werden) und ermöglicht die Verwendung solcher Speicher auch als Programm-Speicher.

Durch die Anforderung nach einer geringen Anzahl von Anschlußleitungen, müssen Adressen und Daten auf die verfügbaren Leitungen durch ein Multiplex-Verfahren bestmöglich verteilt werden. Dazu kommt die Notwendigkeit die bei parallelen Speichern existierenden, zusätzlichen Daten- bzw. Adress-Steuerleitungen (Strobes) durch eine entsprechende “Fluss-Steuerung” für die Datenübertragung zu ergänzen und ein sogenanntes “Command” (Information über die Art des gewünschten Datentransfers) einzuführen.

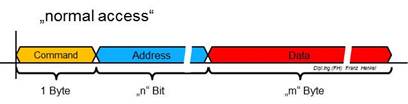

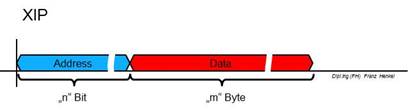

Werden diese Segmente in eine geeignete Reihenfolge gebracht, ergibt sich das prinzipelle Datenprotokoll für einen seriellen Speicher:

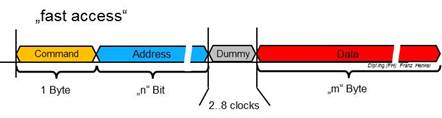

Eine Ausnahme von der oben beschriebenen Struktur bildet der “Fast Access” Modus, der zusätzliche “Dummy” Zyklen (als eine Art “WAIT State”) zwischen dem Adressfeld und dem Datenfeld einfügt aber dafür einen höheren Bus-Takt ermöglicht:

Der “Fast Access” Modus kann in allen Standard Betriebsmodi mit einem, zwei oder vier Datenleitungen, als auch im reinen SPI Mode (unidirektionale Datenleitungen) oder in den später noch beschriebenen I/O-Modi verwendet werden. Definitiv gebraucht wird er meist im XIP-Modus.

Generell werden alle Transfers durch das “deaktivieren” (“high” Pegel) der “Chip Select” Leitung beendet.

Kommandos, Addressen und Daten Werte werden, in allen Modis, mit den “höherwertigen Bits” zuerst übertragen.

Bei der Verwendung von parallelen Datenleitungen werden die in einem Takt parallel übertragenen Bits entsprechend ihrer höheren Wertigkeit auf den höherwertigen Datenleitungen übertragen, heißt das aktuell übertragene höchstwertige Bit wird auf der Datenleitung DQ3, das nächstwertige Bit auf der Datenleitung DQ2 usw. übertragen.

Das Dual SPI Interface überträgt das höherwertige Bit auf DQ1 und das niedrigerwertige Bit auf DQ0.

![]()

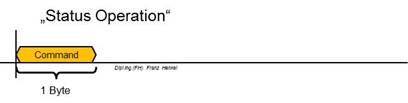

Kommandos sind immer 1 Byte lang und markieren den Start einer Übertragungssequenz. Die verwendeten Kommandos sind üblicherweise bei allen Herstellern von SQI-Speichern identisch, Ausnahmen und besondere Kommandos sind möglich (siehe auch Liste der Kommandos am Ende dieses Dokuments).

Kommandos steuern nicht nur den Datenfluß sondern werden auch verwendet um den Speicherbaustein zu konfigurieren, Datenbereiche zu schützen oder sogenanntes “BOOT”-Bereiche zu definieren.

![]()

Adressen sind je nach Größe des Speichers 3 Byte (bis 16 Mbyte Speichergrösse) bzw. 4 Byte (bis zu 4 GByte) lang.

Ob eine 3 oder 4 Byte Adresse verwendet wird ist implizit im Kommando kodiert, d.h. es gibt spezielle Kommandos die eine 3-Byte Adresse bzw. eine 4-Byte Adresse benötigen. Natürlich muß die jeweilige Adressierungsart vom Speicher-Baustein unterstützt werden.

![]()

Das Datenfeld enthält die effektiven Daten die entweder vom Speicher gelesen oder in den Speicher geschrieben werden. Es kann aber auch Daten enthalten die als Ziel ein Status- oder Kontroll-Register im Speicherbaustein haben.

Bei einem Zugriff auf die Speichermatrix (Inhalt des Speichers) gibt es nahezu keine Beschränkung für die Länge des Datenfeldes da der gesamte Inhalt des Speichers in einem kontinuierlichen Datentransfer gelesen oder geschrieben werden kann.

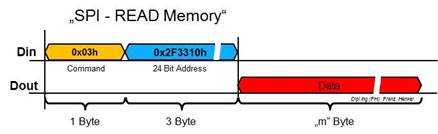

Der standard SPI Mode verwendet “DQ0” als seriellen Eingang “SI” (Din) und “DQ1” ist definiert als serieller Ausgang “SO” (Dout). In diesem Modus und nur in diesem Modus arbeiten die beiden Datenleitungen unidirektional.

“Din” empfängt Kommandos, Addressen und Daten vom Prozessor, während “Dout” Daten vom Speicher oder von den internen Registers des Bausteins an das steuernde System übermittelt.

In oben aufgeführten Beispiel bedeutet das Kommando “0x03h” – “Lesen” von der Adresse “0x2F3310h” (3 Byte Adresse) und die ausgelesenen Daten werden auf der Dout Leitung zur Verfügung gestellt. Es ist Sache des SQI-Controllers (auf der CPU) weitere Taktsignale zu generieren um das nächste Datum aus “0x2F3311h” zu lesen oder die Chip Select Leitung zu deaktiviern um den Übertragungsvorgang abzubrechen.

Unter Verwendung des Kommandos “0x13h” wird eine 4 Byte lange Adressierung für Speicher über 16 Mbyte durchgeführt.

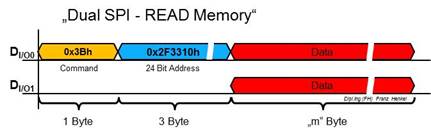

Um gegenüber dem SPI Modus einen Vorteil zu erzielen werden im Dual SPI Mode beide Datenleitungen im bidirektionalen Betrieb verwendet. Speziell bei Speichern, die üblicherweise die Daten in Blöcken (Pages) lesen, erzielt man damit beinahe eine Verdopplung des Datendurchsatzes. Der Dual SPI Lese-Befehl verwendet den Code “0x3Bh”.

In diesem Modus werden die Kommandos und die Adressen weiterhin nur auf der Datenleitung (DI = DQ0), wie im SPI Mode übermittelt. Die Beibehaltung dieser Verfahrensweise ermöglicht einen nahtlosen Übergang zwischen SPI und Dual SPI Modus.

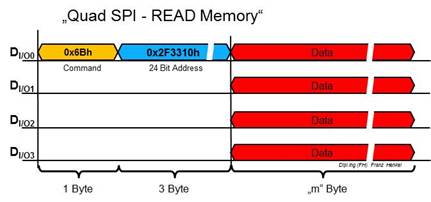

Durch die Verwendung aller vier, in der SQI Spezifikation enthaltenen Datenleitungen lässt sich eine noch höhere Bandbreite für die Übertragung erzielen. Die reine Transferleistung für Daten vervierfacht sich dabei.

Auch für den Quad SPI Modus wird ein spezieller Lese-Befehl verwendet (“0x6Bh”) der ebenso wie der SPI und der Dual SPI Befehl und die darauf folgende Adresse weiterhin über eine Datenleitung übertragen wird. Die eigentlichen Daten werden nach diesem Befehl aber über alle vier Datenleitungen verteilt gesendet (DQ0, DQ1, DQ2, DQ3).

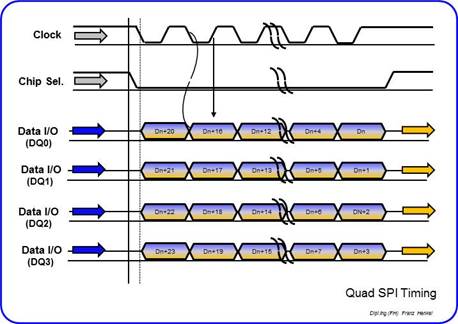

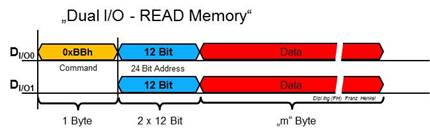

Der “Dual I/O Mode” stellt den nächsten logischen Schritt dar den Datendurchsatz weiter zu erhöhen. Bei Speichern die mit 3 Byte oder 4 Byte langen Adressen arbeiten werden entsprechend 24 oder 32 Taktzyklen alleine für die Übertragung der Adresse benötigt. Im Dual I/O Mode wird die Adresse, genauso wie die Daten über beide Datenleitungen übertragen was die Zeit für den Adresstransfer halbiert.

Der Dual I/O Modus behält die Kompatibilität zu allen vorher besprochenen Modi durch die Übertragung des Kommandos (Befehl “0xBBh”) auf der niedrigstwertigen Datenleitung. Speicher-ICs die den Dual I/O Modus unterstützen erwarten dabei die Adresse auf beiden Datenleitungen.

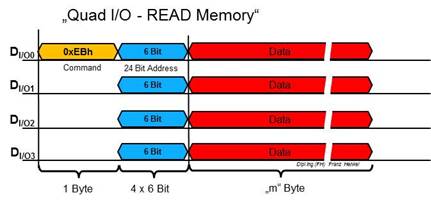

Durch die Erweiterung der Dual I/O Struktur auf alle vier Datenleitungen entsteht der Quad I/O Modus. Jetzt wird das Adressfeld auf allen vier Leitungen übertragen was den Adresstransfer noch einmal beschleunigt. In nachfolgendem Beispiel einer 24 Bit Adresse wird diese in 6 Taktzyklen übertagen.

Der Quad I/O Modus ist der “schnellste” Übertagungsmodus der gegenüber allen vorher erwähnten Modi noch kompatibel ist und sich alleine durch den Befehlscode (“0xEBh”) aufrufen lässt.

Bei manchen Speichern muß dieser Modus aber in einem Status-Register gezielt freigeschaltet werden.

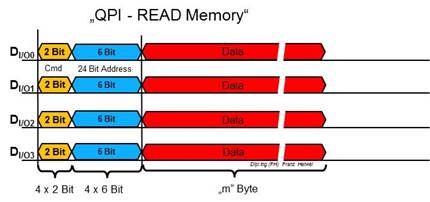

Nachdem sequenziell alle Datenleitungen für die Übertragung der Daten und danach auch für die der Adressen Verwendung fanden, scheint es ein kleiner Schritt zu sein jetzt auch das Kommando über alle vier Leitungen zu übertragen – aber ……

Der Speicher erwartet bisher die Kommandos immer über eine Datenleitung. Würden die Kommandos jetzt plötzlich verteilt auf die verfügbaren Datenleitungen übertragen , so würde der Speicher diese falsch interpretieren. Der einzige Weg den Modus in geordneter Weise zu ändern besteht darin dem Speicher mitzuteilen das ab dem jetzigen Zeitpunkt die Befehle auf alle vier Datenleitungen verteilt übertragen werden.

Für diesen Zweck muß der Speicher in den QPI Mode umgeschaltet werden. Dafür gibt es einen eigenen Befehl “Switch to QPI” (“0x38h” – immer noch auf einer Datenleitung übertragen). Nach diesem Befehl wird der Speicher nicht mehr auf Befehle reagieren die nur über eine Leitung übertragen werden, d.h. alle bisher besprochenen Modi funktionieren nicht mehr. Die steuernde SQI Schnittstelle (z.B. im Microcontroller) muß nach dem Absenden des Befehls alle weiteren Befehle nun im “QPI Mode” übermitteln.

Hier sei noch erwähnt das alle “Quad”-Modi zusätzlich das Setzen eines “Quad enable” Bits in einem Kontroll-Register des Speichers benötigen.

Die Verteilung des Kommandos auf die verfügbaren Datenleitungen bringt für die Übertragung eines Kommandos keinen grossen Vorteil solange der Speicher in Blöcken (Pages) gelesen wird, da dafür ja nur ein Kommando nötig ist. Werden Daten aber in zufälligen Folgen und Byte-bzw. Wort-weise gelesen, so erhöht sich der Datendurchsatz im QPI Modus doch erheblich.

Um den QPI Modus abzuschliessen sei noch erwähnt das durch den Befehl “0xFFh” der QPI Modus wieder abgeschaltet werden kann und der Speicher dann wieder zur bekannten Methode der Kommando-Übermittlung über eine Datenleitung und damit auch zur Kompatibilität zu alle anderen Modi zurückkehrt.

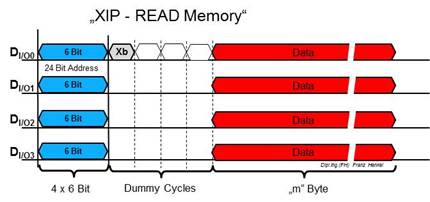

Eingangs wurde bereits erwähnt das durch die neu eingeführten Geschwindigkeitsvorteile, serielle Flash-Speicher jetzt auch für das Speichern und Lesen von Instruktionen für Mikroprozessoren im Betrieb geeignet sind. Der dabei angewandte Modus wird als “XIP” bezeichnet (e Xecute In Place) und besitzt einige Besonderheiten.

Bei den bisher für solche Aufgaben genutzten Speichern mit parallelem Interface läuft zwischen dem Prozessor und dem Speicher eine Sequenz aus Adressübermittlung und Instruktionsübergabe in abwechselnder Reihenfolge. Bei den SQI-Flash Speicher haben wir aber immer einen zusätzlichen Zyklus für die Kommando-Übergabe benötigt, was den Anforderungen für einen Programmspeicher widerspricht.

Zur Lösung dieses Problems wurde bei SQI-Flash Speichern der sogenannte “XIP” Mode eingeführt, der exakt die geforderte Sequenz einhält. Natürlich muss auch hier dem Speicher mitgeteilt werden dass die Interface-Sequenz geändert werden muss. Dies kann im Betrieb durch das Setzen eines Bits im internen Register des Speichers erfolgen. Wird dieses Bit im “none-volatile” (nichtflüchtigen) Register des Speichers gesetzt so wird der Speicher nach einem Reset (bzw. Power On Reset) unmittelbar mit dem XIP Mode starten und damit einen Bootvorgang für den Mikroprozessor ermöglichen.

Im XIP Modus werden immer nur Lesevorgänge ausgeführt, deshalb ist ein spezielles Kommando dafür nicht nötig. Die vom Prozessor übermittelten Daten werden immer als Adresse interpretiert.

Zusätzlich verwendet der XIP Mode immer die “Fast Access” Struktur, dabei bietet sich die Möglichkeit durch die zusätzlichen “Leerzyklen” (Dummy Cycle) dem Speicher zu signalisieren ob dieser weiter im XIP Modus arbeiten oder zu den SPI Modi zurückkehren soll.

Das Xb-Bit gesteuert vom Prozessor auf der Datenleitung DQ0 (DI/O0) signalisiert im ersten Dummy Zyklus ob der Speicher im XIP Modus weiterarbeiten soll (Xb = 0) und eingehende Daten zu Beginn des nächsten “Chip Select” Zyklus weiter als Adressen interpretiert oder ob der Speicher in den SPI Modus zurückkehren soll (Xb = 1) und eingehende Daten als Kommando interpretiert werden müssen.

Natürlich ist auch hier ein sequenzieller Lesevorgang durch weitere vom Prozessor übermittelte Takte innerhalb eines “Chip Select” Zyklus (vor dem deaktivieren des Chip Select) gegeben und damit kann beispielsweise in Verwendung mit einem Cache- oder Page-Speicher im SQI-Kontroller ein schnelles Auffüllen der Daten (Instruktionen) für den Prozessor erreicht werden.

Der XIP Mode kann im laufenden Betrieb durch Schreiben in das “volatile” (flüchtige) Status-Register aktiviert werden. Er kann mit einer, zwei oder vier Datenleitungen konfiguriert werden benutzt aber immer den “Fast Access” Modus.

INFO: Nicht alle kommerziell verfügbaren SQI Speicher unterstützen den XIP Modus und die ICs die den Modus unterstützen, können sich hinsichtlich der Aktivierung bzw. der Registerstruktur unterscheiden.

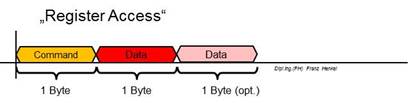

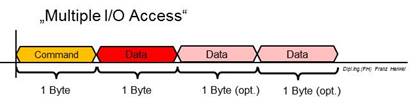

Neben der Speichermatrix besitzen serielle Flashspeicher zusätzliche Register oder Speicherbereiche auf die zugegriffen werden kann. Diese Art von Zugriffen unterscheiden sich von Speicherzugriffen nur durch den Befehls-Code (OpCode) und die Datenstruktur.

Wie bereits angeschnitten werden interne Register verwendet um die Betriebsmodi zu verändern oder um Speicherbereiche vor Veränderungen zu schützen. Es gibt “volatile” Register die ihren Inhalt bei Spannunsgverlust verlieren als auch “none volatile” Register die enthaltene Daten auch ohne Versorgungsspannung behalten. Diese Register können durch spezielle Kommandos beschrieben oder gelesen werden und benutzen implizite Adressierung wie: “0x05h” = Read Status Register 1.

Die Register bezogenen Befehle arbeiten in allen Modi außer im XIP Modus, da hier ja kein Kommando interpretiert wird. Die Datenfelder beinhalten die Daten die in die Register geschrieben bzw. aus den Registern gelesen werden. Register können 8-Bit oder 16-Bit breit sein und der passende Datentransfer muß vom Prozessor richtig gesteuert werden.

Serielle Flash Speicher beinhalten Informationen über den Hersteller, den Speichertyp, Speichergrösse etc. die helfen im Betrieb das jeweilige IC zu identifizieren. Diese Daten sind nur lesbar und werden vom Hersteller während des Fertigungsprozesses in das Bauteil geschrieben.

Diese Informationen können wie die Inhalte der Register über dedizierte Befehle gelesen werden, als Beispiel sei hier der Befehl “0x90h” = Read Manufacturer ID genannt

Die meisten heute üblichen seriellen Flash-Speicher beinhalten neben der Speichermatrix auch einen kleinen Bereich der nicht löschbar ist. Diese OTP Zellen (one time programmable) werden ebenfalls über spezielle Befehle angesprochen.

Die Grösse des OTP-Bereichs liegt üblicherweise bei 64 bis zu 256 Byte und dient zum Speichern gerätespezifischer Daten die nur einmal abgelegt werden müssen und unveränderbar sein sollen (Serien Nummer, Address-IDs usw.)

Die entsprechenden Befehle für das OTP Array sind “Program OTP Array” bzw. “Read OTP Array”, wobei es natürlich keinen Befehl für das Löschen gibt.

Auch bei diesen Befehlen ist die Adresse teil des OpCodes und wird für die einzelnen Bytes automatisch incrementiert.

Wir haben das Kommando “0x38h” (Enable QPI Mode) bereits angesprochen. Solche Befehle beinhalten keine Daten sondern setzen den Baustein in einen besonderen Zustand, daher handelt es sich hier um einzelne 1 Byte lange Befehle.

|

Command |

Code |

Addr. Bytes |

Data Bytes |

Comment |

|

|

Write Status Register |

0x01h |

0 |

1 (2) |

|

|

|

Page Program |

0x02h |

3 |

1 .. 256 |

Can be single, dual or quad Data |

|

|

Read |

0x03h |

3 |

1 .. max. |

“max.” = max Memory Address |

|

|

Write Disable |

0x04h |

0 |

0 |

Write Protection set |

|

|

Read Status Register 1 |

0x05h |

0 |

1 |

|

|

|

Write Enable |

0x06h |

0 |

0 |

Write Protection reset |

|

|

Read Status Register 2 |

0x07h |

0 |

1 |

|

|

|

Fast Read |

0x0Bh |

3 |

1 .. max. |

“max.” = max Memory Address |

|

|

0x0Ch |

4 |

1 .. max. |

“max.” = max Memory Address |

||

|

Fast Read DDR |

0x0Dh |

3 |

1 .. max. |

“max.” = max Memory Address |

|

|

0x0Eh |

4 |

1 .. max. |

“max.” = max Memory Address |

||

|

Ext. Quad Fast Program |

0x12h |

4 |

1 .. 256 |

Also for DDR Page Program |

|

|

Read |

0x13h |

4 |

1 .. max. |

“max.” = max Memory Address |

|

|

AutoBoot Register Read |

0x14h |

0 |

1 |

|

|

|

AutoBoot Register Write |

0x15h |

0 |

1 |

|

|

|

Bank Register Read |

0x16h |

0 |

x |

|

|

|

Bank Register Write |

0x17h |

0 |

x |

|

|

|

Fast Read |

0x1Bh |

3 |

1 .. max. |

“max.” = max Mem , 2 Dummy |

|

|

Subsector Erase |

0x20h |

3 |

0 |

4 kB |

|

|

0x21h |

4 |

0 |

|

||

|

Read ASP |

0x2Bh |

|

|

|

|

|

Program ASP |

0x2Fh |

|

|

|

|

|

Clear Status Register 1 |

0x30h |

0 |

0 |

|

|

|

Write Status Register 2 |

0x31h |

0 |

1+ |

“ATMEL” 25DQ161 |

|

|

Quad Input Fast Program |

0x32h |

3 |

1 .. Page |

SPI or Ext. SPI mode, 256Byte |

|

|

Sector Lock Down |

0x33h |

3 |

1 |

|

|

|

Quad Page Program |

0x34h |

4 |

1 .. Page |

|

|

|

Freeze Sector Lockdown |

3 |

1 |

“ATMEL” AT25DQ161 |

||

|

Read Configuration Reg. 1 |

0x35h |

0 |

1 |

Alt: Read Status Reg. 2 |

|

|

Protect Sector |

0x36h |

3 |

0 |

|

|

|

Enable QPI Mode |

0x38h |

0 |

0 |

|

|

|

Unprotect Sector |

0x39h |

3 |

0 |

|

|

|

Dual Output Fast Read |

0x3Bh |

3 |

1 .. max. |

“max.” = max Memory Address |

|

|

0x3Ch |

4 |

1 .. max. |

“max.” = max Memory Address |

||

|

Read Sector Prot. Reg. |

3 |

1+ |

“ATMEL” AT25DQ161 |

||

|

Data Learning Pattern Read |

0x41h |

|

|

|

|

|

Program OTP Array |

0x42h |

3 |

1.. max.OTP |

Alt: Security Registers |

|

|

Prog.NV Data Learning Reg. |

0x43h |

|

|

|

|

|

|

0x44h |

3 |

|

|

|

|

Write Volat. Data Learn Reg. |

0x4Ah |

|

|

|

|

|

Read OTP Array |

0x4Bh |

|

1.. max.OTP |

Alt: Unique ID = 8 Byte |

|

|

Clear Flag Status Register |

0x50h |

0 |

0 |

Alt: Volatile SR Write Enable |

|

|

Block Erase |

0x52h |

3 |

0 |

32kB |

|

|

Read Discovery Parameter |

0x5Ah |

|

1 .. max. |

“max.” = max Memory Address |

|

|

Bulk Erase (Chip Erase) |

0x60h |

0 |

0 |

|

|

|

Write Enh. Volatile CFG Reg. |

0x61h |

|

1 |

|

|

|

Read Enh. Volatile CFG Reg. |

0x65h |

|

1 .. max. |

“max.” = max Memory Address |

|

|

Reset Enable |

0x66h |

0 |

0 |

|

|

|

Quad Output Fast Read |

0x6Bh |

3 |

1 .. max. |

“max.” = max Memory Address |

|

|

Read Flag Status Register |

0x70h |

|

1 .. max. |

“max.” = max Memory Address |

|

|

Program/Erase Suspend |

0x75h |

0 |

0 |

|

|

|

Set Burst Wrap |

0x77h |

0 |

1 |

|

|

|

Read OTP Security Reg. |

3 |

1+ |

“ATMEL” AT25DQ161 |

||

|

Program/Erase Resume |

0x7Ah |

0 |

0 |

|

|

|

Write Volatile CFG Reg. |

0x81h |

0 |

1 |

|

|

|

Read Volatile CFG Reg. |

0x85h |

0 |

1 .. max. |

|

|

|

Program Suspend |

0x85h |

0 |

0 |

|

|

|

Program Resume |

0x8Ah |

0 |

0 |

|

|

|

Read Manufacturer ID |

0x90h |

0 |

1 (2) |

MF-Byte + ID-Byte |

|

|

|

0x92h |

0 |

1 |

|

|

|

Read Manufacturer ID Dual |

0x92h |

0 (1) |

1 (2) |

|

|

|

Read Manufacturer ID Quad |

0x94h |

3 |

2 |

|

|

|

Reset Memory |

0x99h |

0 |

0 |

|

|

|

Progr. OTP Security Reg. |

0x9Bh |

3 |

1+ |

|

|

|

Read ID |

0x9Eh |

0 |

1 .. 20 |

|

|

|

Read ID |

0x9Fh |

0 |

2 (3) |

JEDEC ID |

|

|

Dual Input Fast Program |

0xA2h |

3 |

1 .. 256 |

Can be single, dual or quad Data |

|

|

Reserved |

0xA3h |

|

|

|

|

|

Write PPB Lock Bit |

0xA6h |

|

|

|

|

|

Read PPB Lock Bit |

0xA7h |

|

|

|

|

|

Read Electronic Signature |

0xABh |

0 |

1 |

Alt: Release Power Down |

|

|

Multiple I/O Read ID |

0xAFh |

|

1 .. 3 |

|

|

|

Program Erase/Suspend |

0xB0h |

0 |

0 |

|

|

|

Write Nonvolatile CFG Reg. |

0xB1h |

|

2 |

|

|

|

Read Nonvolatile CFG Reg. |

0xB5h |

|

2 |

|

|

|

Bank Register Access |

0xB9h |

0 |

0 |

Power Down |

|

|

Dual I/O Fast Read |

0xBBh |

3 |

1 .. max. |

“max.” = max Memory Address |

|

|

0xBCh |

4 |

1 .. max. |

“max.” = max Memory Address |

||

|

Dual I/O Fast Read DDR |

0xBDh |

3 |

1 .. max. |

“max.” = max Memory Address |

|

|

0xBEh |

4 |

1 .. max. |

“max.” = max Memory Address |

||

|

Program/Erase Resume |

0xD0h |

0 |

0 |

|

|

|

Sector Erase |

0xD8h |

3 |

0 |

64k Erase |

|

|

0xDCh |

4 |

0 |

|

||

|

Set Read Parameters |

0xC0h |

0 |

1 |

|

|

|

Bulk Erase (Chip Erase) |

0xC7h |

0 |

0 |

Alternative to Command 0x60h |

|

|

Read DYB |

0xE0h |

|

|

|

|

|

Write DYB |

0xE1h |

|

|

|

|

|

Read PPB |

0xE2h |

|

|

|

|

|

Program PPB |

0xE3h |

|

|

|

|

|

Erase PPB |

0xE4h |

|

|

|

|

|

Write Lock Register |

0xE5h |

|

1 |

|

|

|

Reserved |

0xE6h |

|

|

|

|

|

Read Password |

0xE7h |

0 |

x |

|

|

|

Read Lock Register (Password) |

0xE8h |

|

1 .. max. |

“max.” = max Memory Address |

|

|

Unlock Password |

0xE9h |

|

|

|

|

|

Quad I/O Fast Read |

0xEBh |

3 |

1 .. max. |

“max.” = max Memory Address |

|

|

0xECh |

4 |

1 .. max. |

“max.” = max Memory Address |

||

|

Quad I/O Fast Read DDR |

0xEDh |

3 |

1 .. max. |

“max.” = max Memory Address |

|

|

0xEEh |

4 |

1 .. max. |

“max.” = max Memory Address |

||

|

Reset |

0xF0h |

0 |

0 |

|

|

|

Mode Bit Set |

0xFFh |

0 |

0 |

|

|

Hinweis: OpCodes oder deren Funktion können bei verschiedenen Herstellern unterschiedlich sein !

Copyright 2016 by Dipl.Ing.(FH) Franz Henkel

Dieses Dokument sowie dessen Inhalt, insbesondere Texte, Fotografien und Grafiken, unterliegt dem Copyright (© 2016) und sind nur mit einer schriftlicher Zustimmung des Autors, Dipl.Ing.(FH) Franz Henkel zur vollständigen oder auszugsweisen Weiterverwendung in Form einer gedruckten oder elektronischen Kopie oder Replikation bzw. einer vollständigen oder auszugsweisen Bereitstellung des Inhalts in schriftlicher, gedruckter oder elektronischer Form, zu verwenden.