|

|

AQM8S105 Modul

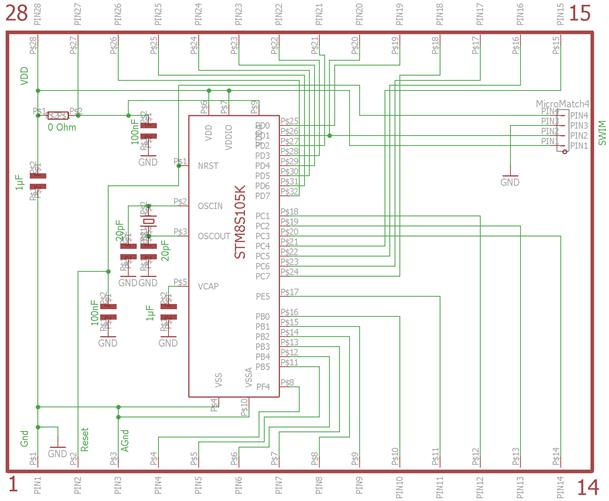

Das AQM8S105 Modul ist auf einem 28-pin Dual-In-Line Trägersockel aufgebaut und umfasst alle nötigen externen Komponenten für den STM8S105 Microcontroller. Zum Betrieb muss lediglich die Versorgungspannung angeschlossen werden und das Modul wird das, im internen Flash-Speicher des STM8S105 abgelegte Programm, auszuführen. Das System arbeitet mit dem auf dem Modul befindlichen 16 MHz Quarz oder dem STM8-internen Oszillator, daher ist keine weitere Taktquelle erforderlich.

|

|

Der 8 Bit Mikrokontroller STM8S105K im 32 Pin LQFP32 Gehäuse ist das Kernstück des AQM8S105 Moduls.

Der Kontroller besitzt folgende integrierte Speicher für das Programm und für die Daten:

Die primäre Takterzeugung erfolgt auf dem Modul und benutzt den 16 MHz Quarz als präzise Taktquelle.

Neben den üblichen Ein-/Ausgängen sind folgende Schnittstellen und Funktionsblöcke verfügbar:

Alle Anschlüsse für spezielle Funktionen sind mit GPIO Pins gemultiplexed und stehen gegebenenfalls nicht parallel zur Verfügung.

Das Modul ist in einem 28-pin Dual-In-Line Format aufgebaut und die Leiterplatte ist mit einem doppel-seitigen Stiftsockel verbunden. Alle Komponenten sind auf der Oberseite des Moduls montiert.

Der 28-pin Sockel ermöglicht die Verbindung der Versorgungsspannung und aller Ein-/Ausgänge. Auf dem Modul stehen bis zu 23 universelle Ein-/Ausgänge (GPIO) zur Verfügung. Die Pin-Nummern werden in der üblichen Zählweise, mit Pin 1 links/unten (in obigen Bild) gezählt. Der Sockel bietet zur Orientierung einen halbkreisförmigen Ausschnitt auf der Seite mit dem Pin 1 um ein falsches anschliessen zu vermeiden. Der Trägersockel bietet qualitative hochwertige, gedrehte und vergoldete Pins um einen zuverlässigen Kontakt zu einem Sockel zu ermöglichen. Das Modul kann aber ebenso gut direkt in eine Leiterplatte eingelötet werden.

| System Verbinder (28 Pin DIL) | ||||

| Pin | Signal | Signal Art | Nom. Wert | Alt. Funktion |

| 1 | Masse (VSS) | Versorgung | 0 Volt | |

| 2 | System Reset (NRST) | Eingang | Aktiv “low” | |

| 3 | Analog Masse (VSSA) | Versorgung | 0 Volt | |

| 4 | I/O Port PF4 | I/O | Logic Lvl | Analog Eingang AIN12 |

| 5 | I/O Port PB5 | I/O | Logic Lvl | Analog Eingang AIN5 / I²C-SDA |

| 6 | I/O Port PB4 | I/O | Logic Lvl | Analog Eingang AIN4 / I²C-SCL |

| 7 | I/O Port PB3 | I/O | Logic Lvl | Analog Eingang AIN3 / TIM1-ETR |

| 8 | I/O Port PB2 | I/O | Logic Lvl | Analog Eingang AIN2 / TIM1-CH3N |

| 9 | I/O Port PB1 | I/O | Logic Lvl | Analog Eingang AIN1 / TIM1-CH2N |

| 10 | I/O Port PB0 | I/O | Logic Lvl | Analog Eingang AIN0 / TIM1-CH1N |

| 11 | I/O Port PE5 | I/O | Logic Lvl | SPI-NSS |

| 12 | I/O Port PC1 | I/O (HS*) | Logic Lvl | TIM1-CH1 / UART2-CK |

| 13 | I/O Port PC2 | I/O (HS*) | Logic Lvl | TIM1-CH2 |

| 14 | I/O Port PC3 | I/O (HS*) | Logic Lvl | TIM1-CH3 |

| 15 | I/O Port PC4 | I/O (HS*) | Logic Lvl | TIM1-CH4 |

| 16 | I/O Port PC5 | I/O (HS*) | Logic Lvl | SPI-CLK |

| 17 | I/O Port PC6 | I/O (HS*) | Logic Lvl | SPI-MOSI |

| 18 | I/O Port PC7 | I/O (HS*) | Logic Lvl | SPI-MISO |

| 19 | I/O Port PD0 | I/O (HS*) | Logic Lvl | TIM3-CH2 / TIM1-BKIN |

| 20 | I/O Port PD1 | I/O (HS*) | Logic Lvl | SWIM (Debug Pin) |

| 21 | I/O Port PD2 | I/O (HS*) | Logic Lvl | TIM3-CH1 / TIM2-CH3 |

| 22 | I/O Port PD3 | I/O (HS*) | Logic Lvl | TIM2-CH2 / ADC-ETR |

| 23 | I/O Port PD4 | I/O (HS*) | Logic Lvl | TIM2-CH1 / BEEP |

| 24 | I/O Port PD5 | I/O | Logic Lvl | UART2-TX |

| 25 | I/O Port PD6 | I/O | Logic Lvl | UART2-RX |

| 26 | I/O Port PD7 | I/O | Logic Lvl | TIM1-CH4 |

| 27 | Betriebsspannung (VDDA) | Versorgung | 3.0 .. 5.5 V | Muss mit VDD verbunden werden |

| 28 | Betriebsspannung (VDD) | Versorgung | 2.95 .. 5.5 V | 3.3V or 5.0V / ±10% |

*) HS = High Sink Current

Der 4-polige “SWIM” Anschluss ermöglicht die direkte Verbindung zu einem „Debug“-Interface. Über diesen Stecker können die Binär-Files in den nicht flüchtigen Programmspeicher des Prozessors geladen werden. Auch die „Debug“ Daten werden über dieses Interface zwischen dem Modul und dem PC übertragen.

| SWIM Connector (MicroMatch) | ||||

| Pin | Signal | Richtung | Wert | Alt. Funktion |

| 1 | Supply (VDD) | Supply | 3.3/5.0V | |

| 2 | SWIM | I/O | SWIM Interface Data Line | |

| 3 | Ground (VSS) | Supply | 0 V | |

| 4 | System Reset (NRST) | Input | “High” Pegel | Reset wird durch “low” Pegel aktiv |

|

|

Der 4-pin “MicroMatch” Steckverbinder ist eine eigenständige Lösung für den “Debug”-Anschluß des STM8S105 auf dem Modul. Die Pin-Belegung ist so gewählt dass ein entsprechendes Adapterkabel zum gebräuchlichen Debug-Interface mit einem 4-poligen Flachbandkabel hergestellt werden kann. Der Pin 1 des Steckers ist durch eine „Index“-Bohrung auf dem Modul gekennzeichnet und verhindert so ein um 180° gedrehtes einstecken.

|

|

|

| Parameter | Konditionen | Min. | Typ. | Max. | Einheit |

| Temperatur Bereich | -20 | +70 | °C | ||

| Versorgungsspannung | VDD | 3.0 | 5.5 | Volt | |

| Stromaufnahme | Details siehe Datenblatt | 8.0 | mA | ||

| Taktfrequenz | Quarz | -150ppm | 16 | +150ppm | MHz |

| Interner "HSI" RC Oszillator | -20°C .. +70°C | 15.68 | 16 | 16,32 | MHz |

| Interner "LSI" RC Oszillator | -20°C .. +70°C | 110 | 128 | 146 | kHz |

| Max. Anzahl von GPIO | Gemultiplexed | 23 | |||

| Max. Anzahl von ADC Eingängen | Gemultiplexed | 7 | |||

| Digitale Eingangsspannung “Low” | 0.0 | 0.3 x VDD | Volt | ||

| Digitale Eingangsspannung “High” | 0.7 x VDD | VDD | |||

| Digitale Ausgangsspannung “Low” | @ 3.3V Supply / 4mA @ 5.0 V Supply / 10mA |

1.0 2.0 |

Volt | ||

| Digitale Ausgangsspannung “High” | @ 3.3 V Supply / 4mA @ 5.0 V Supply / 10 mA |

2.0 2.4 |

Volt | ||

| HS Ausgänge “Low” Level | @ 3.3 V Supply / 10 mA @ 5.0 V Supply / 10 mA @ 5.0 V Supply / 20 mA |

1.1 0.9 1.6 |

Volt | ||

| HS Ausgänge “High” Level | @ 3.3 V Supply / 10 mA @ 5.0 V Supply / 10 mA @ 5.0 V Supply / 20 mA |

1.9 3.8 2.9 |

Volt |

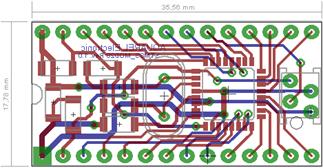

Die verwendete Leiterplatte ist doppelseitig (FR4) mit einseitiger Bestückung. Der Quarz und der „MicroMatch“ Steckverbinder sind konventionell in Leiterplattenbohrungen montiert, alle übrigen Bauteile sind oberfächenmontiert.

Die Leiterplatte ist auf einem 28-Pin DIL Träger entsprechend nachfolgendem Bild montiert.

Das zweiseitige Layout ist in der nachfolgenden Zeichnung dargestellt.

| Nr. | Name | Wert | Typ | RM | Kommentar |

| 1 | C1, C6 | 1µF / 25V | Keramik | 1206 | Keramik Multilayer |

| 2 | C2, C5 | 100nF / 50V | Keramik | 1206 | Keramik Multilayer |

| 3 | C3, C4 | 20pF / 50V | Keramik | 1206 | Keramik |

| 4 | R1 | 0 Ohm | 1206 | ||

| 5 | X1 | 16 Mhz Quarz | HC49U | RM5.0 | |

| 6 | IC1 | STM8S105K | LQFP32 | STMicroelectronics | |

| 7 | Con 1 | 28 pin DIL Adapter | RM2.54 | AR28 (Source: Reichelt) | |

| 8 | Con 2 | MicroMatch / gerade | 2 x 2 polig | RM1.27 | MM FL 4G (Source: Reichelt) |

| Revision | Author | Datum | Änderungen und Korrektur | |||

|

1.0 |

F.Henkel |

16.12.2013 |

Erste Ausgabe |

|||

|

1.1d |

F.Henkel |

20.3.2015 |

Zusätzliche Bilder, Korrekturen |

|||

|

1.2d |

F.Henkel |

24.5.2016 |

Geändertes SWIM Conn. Bild, 0 Ohm |

|||

|

2.0d |

F.Henkel |

31.5.2016 |

Neue Inhalte |

|||

Dieses Dokument sowie dessen Inhalt, insbesondere Texte, Fotografien und Grafiken, unterliegt dem Copyright (© 2017) und sind nur mit einer schriftlicher Zustimmung des Autors, Dipl.Ing.(FH) Franz Henkel zur vollständigen oder auszugsweisen Weiterverwendung in Form einer gedruckten oder elektronischen Kopie oder Replikation bzw. einer vollständigen oder auszugsweisen Bereitstellung des Inhalts in schriftlicher, gedruckter oder elektronischer Form, zu verwenden.

Alle „Copyright“ Rechte liegen beim Author.